- Nr art. RS:

- 136-8071

- Nr części producenta:

- 410-346-20

- Producent:

- Digilent

2 Dostawa w ciągu 1 dni roboczych. UWAGA: Dostawa może potrwać o 1 dzień roboczy dłużej w zależności od miejsca doręczenia.

7 Dostawa w ciągu 1 dni roboczych. UWAGA: Dostawa może potrwać o 1 dzień roboczy dłużej w zależności od miejsca doręczenia.

Dodano do koszyka

Cena netto za szt.

1 366,20 zł

(bez VAT)

1 680,43 zł

(z VAT)

| Produkty | Per unit |

| 1 - 1 | 1 366,20 zł |

| 2 - 4 | 1 331,23 zł |

| 5 + | 1 297,91 zł |

- Nr art. RS:

- 136-8071

- Nr części producenta:

- 410-346-20

- Producent:

- Digilent

Atesty i certyfikaty

Szczegółowe dane produktu

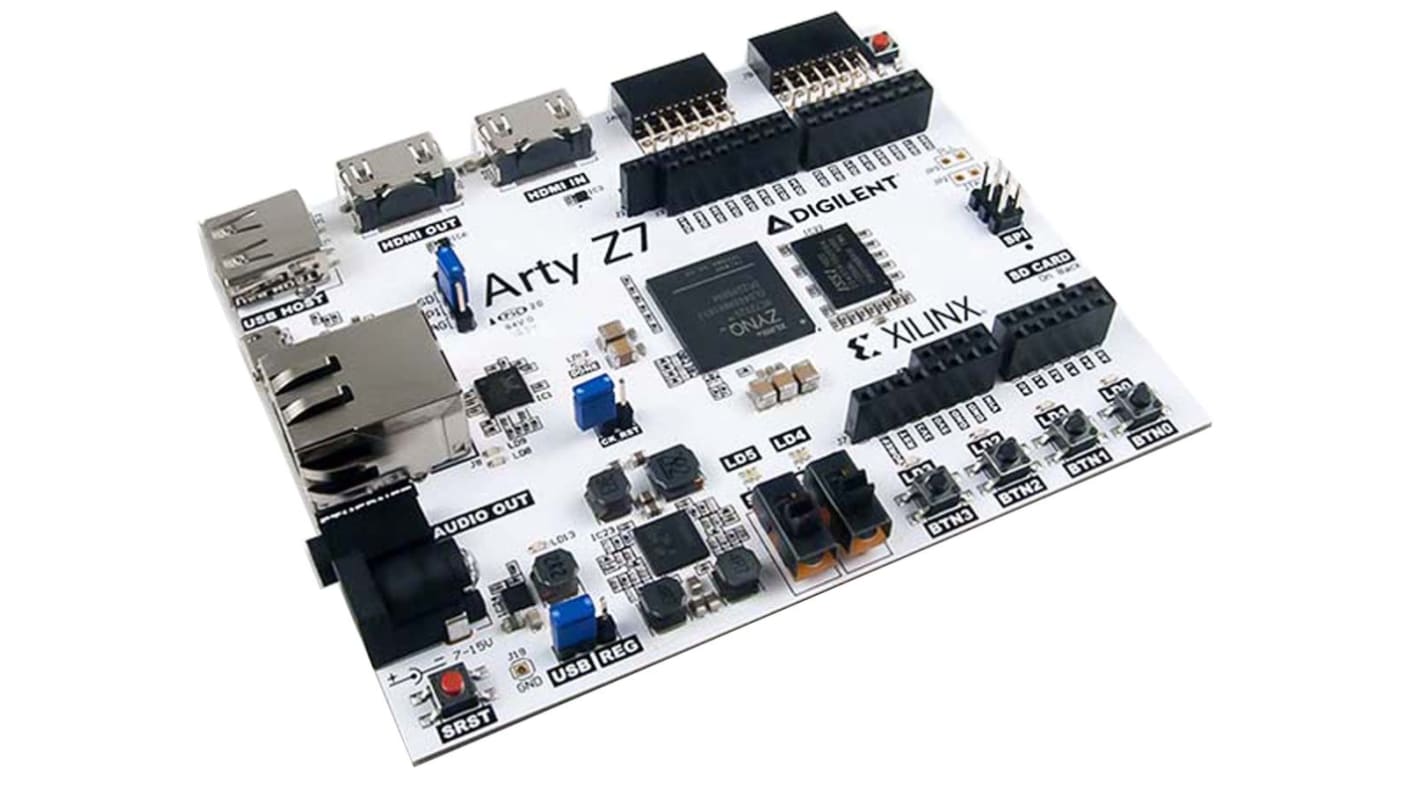

Arty Z7 Wynq-7000 - płyta konstruktorska

Procesor graficzny Z7-20 to platforma projektowa zaprojektowana wokół Xilinx Zynq-7000™ All Programmable System-on-Chip (AP SoC). Architektura Zynq-7000 obejmuje dwurdzeniowy procesor ARM Cortex-A9 650 MHz z układem scalonym Artx-7 serii FPGA. To połączenie oznacza potężny procesor z unikatowym zestawem programowo zdefiniowanych urządzeń peryferyjnych i kontrolerów. Narzędzia Vivado, Petalinux i SDSoC umożliwiają określenie własnego zestawu urządzeń peryferyjnych i dostosowanie jego funkcjonalności do systemu operacyjnego Linux lub programu "goły metal" działającego na procesorze.

Xilinx Zynq-7000 (XC7Z020-1CLG400C)

• Procesor: Rdzeń procesora ARM 650MHz Cortex-A9

• Tablice przeglądowe (LUT): 53200

• Flip-flopy: 106400

• Blokuj pamięć RAM: 630KB

• Wysyłki zarządzania zegarem: 4

• Dostępne wejścia/wyjścia osłony: 49

• Kontroler pamięci DDR3 z 8 kanałami DMA i 4 portami podrzędnymi AXI3

• Wysokiej przepustowości kontrolery urządzeń peryferyjnych: 1G Ethernet, USB 2.0, SDIO

• Niskopasmowy kontroler urządzeń peryferyjnych: SPI, UART, CAN, I²C.

• Programowalne z kart JTAG, Quad-SPI Flash lub microSD

• Oprogramowanie układów logicznych o programowanej pamięci FPGA Artix-7

• Tablice przeglądowe (LUT): 53200

• Flip-flopy: 106400

• Blokuj pamięć RAM: 630KB

• Wysyłki zarządzania zegarem: 4

• Dostępne wejścia/wyjścia osłony: 49

• Kontroler pamięci DDR3 z 8 kanałami DMA i 4 portami podrzędnymi AXI3

• Wysokiej przepustowości kontrolery urządzeń peryferyjnych: 1G Ethernet, USB 2.0, SDIO

• Niskopasmowy kontroler urządzeń peryferyjnych: SPI, UART, CAN, I²C.

• Programowalne z kart JTAG, Quad-SPI Flash lub microSD

• Oprogramowanie układów logicznych o programowanej pamięci FPGA Artix-7

Pamięć i zasilanie płyty głównej

• Wbudowana pamięć DDR3 SDRAM IS43TR16256A-125KBL 512 MB z 16-bitową magistralą @ 1050 Mb/s

• Wbudowana poczwórna lampa błyskowa SPI S25FL128S 16 MB z 48-bitowym, unikatowym identyfikatorem EUI-48/64™

• Gniazdo karty microSD

• Zasilanie z gniazda USB lub napięcia +7V do +15Vdc przez gniazdo cylindryczne

• Wbudowana poczwórna lampa błyskowa SPI S25FL128S 16 MB z 48-bitowym, unikatowym identyfikatorem EUI-48/64™

• Gniazdo karty microSD

• Zasilanie z gniazda USB lub napięcia +7V do +15Vdc przez gniazdo cylindryczne

Połączenia systemowe

• Ethernet 10/100/1000 przez złącze RJ45

• Most USB-UART przez gniazdo micro-B.

• Programowanie przez port USB-JTAG za pośrednictwem gniazda micro-B.

• USB OTG PHY (obsługuje tylko host) poprzez gniazdo USB-A.

• Most USB-UART przez gniazdo micro-B.

• Programowanie przez port USB-JTAG za pośrednictwem gniazda micro-B.

• USB OTG PHY (obsługuje tylko host) poprzez gniazdo USB-A.

Audio i wideo

• Gniazdo radiatora HDMI (wejście)

• Port źródłowy HDMI (wyjście)

• Wyjście monofoniczne napędzane przez PWM za pośrednictwem gniazda 3,5 mm typu jack

• Port źródłowy HDMI (wyjście)

• Wyjście monofoniczne napędzane przez PWM za pośrednictwem gniazda 3,5 mm typu jack

Przełączniki i diody LED

• Przyciski zerowania i programowania

• 4 przyciski użytkownika

• 2 przełączniki slajdów użytkownika

• 4 diody LED użytkownika

• 2 diody LED RGB użytkownika

• 4 przyciski użytkownika

• 2 przełączniki slajdów użytkownika

• 4 diody LED użytkownika

• 2 diody LED RGB użytkownika

Złącza rozszerzeń

• KLEPISK/Arduino R3 z osłonami

• 2 x standardowe złącza 12-stykowe Pmod™

• 2 x standardowe złącza 12-stykowe Pmod™

.

FPGA to urządzenie półprzewodnikowe składające się z Matrix Configurable Logic Blocks (CLB) połączonych przez programowalne łączniki. Użytkownik określa te połączenia poprzez programowanie SRAM. CLB może być prosty (ORAZ, LUB Gates, itp.) lub złożony (blok pamięci RAM). Układ FPGA umożliwia wprowadzanie zmian w konstrukcji nawet po przylutowaniu urządzenia do płytki drukowanej.

Dane techniczne

Atrybut | Parametr |

|---|---|

| Nazwa zestawu | Arty Z7-20 APSoC Zynq-7000 |

| Rodzaj zestawu | Płyta rozwojowa |

- Nr art. RS:

- 136-8071

- Nr części producenta:

- 410-346-20

- Producent:

- Digilent