- Nr art. RS:

- 778-5354

- Nr części producenta:

- DK-DEV-5AGTD7N

- Producent:

- Altera

Produkt wycofany

- Nr art. RS:

- 778-5354

- Nr części producenta:

- DK-DEV-5AGTD7N

- Producent:

- Altera

Atesty i certyfikaty

Szczegółowe dane produktu

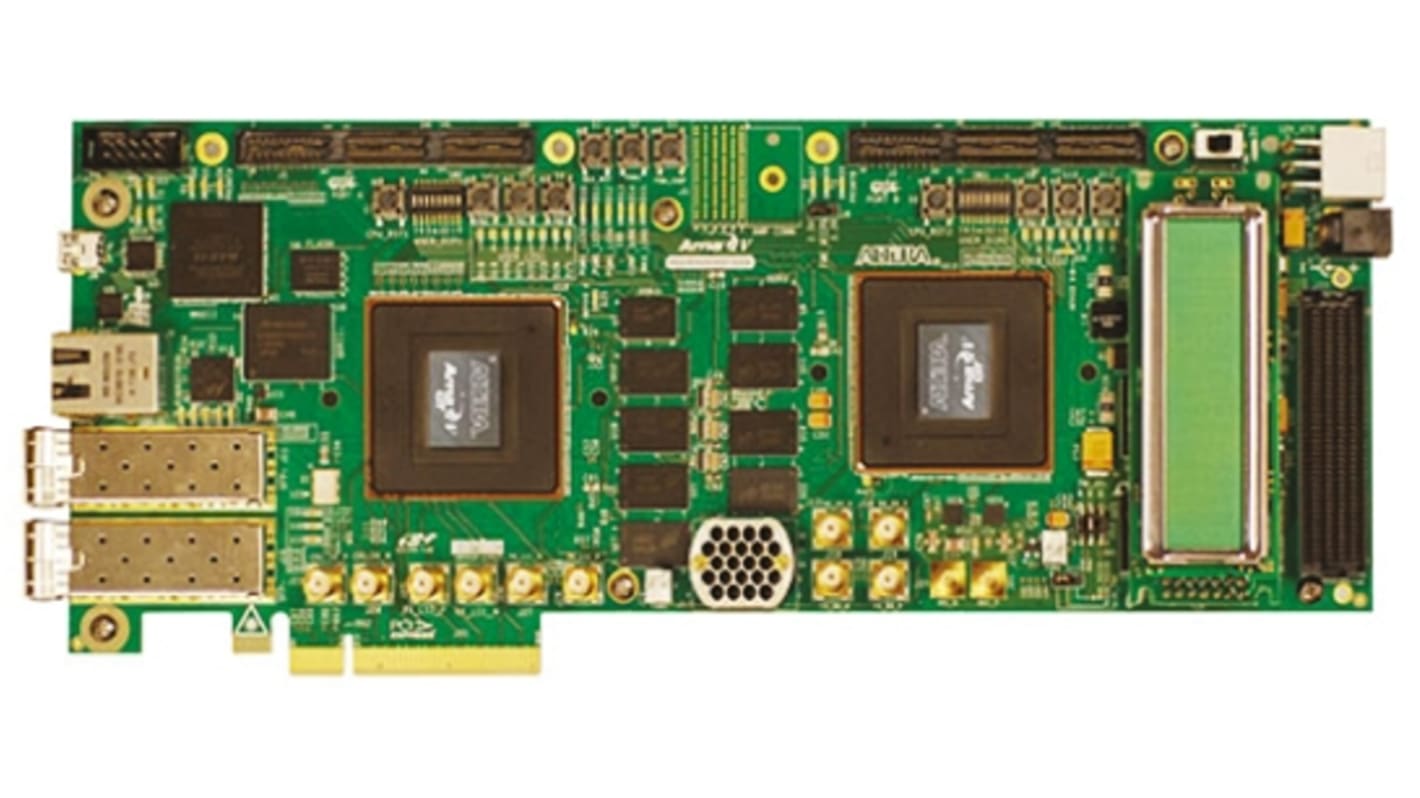

Arria V GT FPGA Development Kit Altera

Altera Arria® V GT FPGA Development Kit zapewnia kompletne środowisko projektowe obejmujące wszystkie elementy sprzętowe i oprogramowanie, które należy opracować i przetestować w środowisku systemowym.

Zespół 1

Aria V GT FPGA: 5AGTFD7K3F40I3N

1152MB x 72 SDRAM DDR3

4,5 MB (1 MB x 36) QDR II+ SRAM

Pamięć flash do synchronizacji z pamięcią 1 Gb (x16)

Złącze krawędziowe PCI Express (PCIe) x8

HSMC Port A (osiem kanałów nadajnika-odbiornika)

USB 2.0

Komunikacja Gigabit Ethernet

Most typu chip-chip z 29 wejściami LVDS, 29 wyjściami LVDS i nadajnikami-odbiornikami x8

2 kanały SFP+

Złącze kamery Bull's Eye (kanał nadajnika-odbiornika 3 x 10 Gb/s)

Złącze SMA (kanał nadajnika-odbiornika 10 Gb/s)

Konfiguracja: JTAG, Parallel Flash Tralover (FPP) z szybkim pasywnym układem hydraulicznym (PFL)

Przyciski, przełączniki, diody LED i wyświetlacze

Przycisk resetowania procesora

3 x przyciski użytkownika

8 mikroprzełączników

16 diod LED użytkownika (w tym osiem diod dwukolorowych)

3 diody LED PCIe

3 diody LED stanu HSMA

Wyświetlacz LCD o przekątnej 2 linii x 16 znaków

Agregat 2

Aria V GT FPGA: 5AGTFD7K3F40I3N

X64 DDR3 SDRAM - kontroler programowy (lub x32 - kontroler IP)

Port HSMC B (cztery kanały nadawczo-odbiorcze)

Port FMC (dziesięć kanałów nadajnika)

Most typu chip-chip z 29 wejściami LVDS i 29 wyjściami LVDS oraz transceiverami x8

Kanał szeregowy interfejs cyfrowy (SDI)

Złącze kamery Bull's Eye (kanał nadajnika-odbiornika o przepustowości 6 Gb/s)

Złącze kamery Bull's Eye (kanał nadajnika-odbiornika 10 Gb/s)

Złącze SMA (kanał nadajnika-odbiornika 10 Gb/s)

Konfiguracja: JTAG, Parallel Flash Tralover (FPP) z szybkim pasywnym układem hydraulicznym (PFL)

Przyciski, przełączniki, diody LED i wyświetlacze

Przycisk resetowania procesora

3 x przyciski użytkownika

8 mikroprzełączników

16 diod LED użytkownika (w tym osiem diod dwukolorowych)

Kontroler systemowy EPM2210GF324

Wbudowany kabel do pobierania USB-Blaster II EPM570GM100

Taktowanie: Oscylator 50 MHz i 145 MHz

Programowalne oscylatory o częstotliwości 100 MHz i 4 wyjścia

Wejście SMA (LVPECL)

Zasilanie: Gniazdo zasilania (prąd stały) laptopa, złącze krawędziowe PCIe

Monitorowanie systemu, zasilanie: (Napięcie, prąd i moc), na jednostkę na szynę

Aria V GT FPGA: 5AGTFD7K3F40I3N

1152MB x 72 SDRAM DDR3

4,5 MB (1 MB x 36) QDR II+ SRAM

Pamięć flash do synchronizacji z pamięcią 1 Gb (x16)

Złącze krawędziowe PCI Express (PCIe) x8

HSMC Port A (osiem kanałów nadajnika-odbiornika)

USB 2.0

Komunikacja Gigabit Ethernet

Most typu chip-chip z 29 wejściami LVDS, 29 wyjściami LVDS i nadajnikami-odbiornikami x8

2 kanały SFP+

Złącze kamery Bull's Eye (kanał nadajnika-odbiornika 3 x 10 Gb/s)

Złącze SMA (kanał nadajnika-odbiornika 10 Gb/s)

Konfiguracja: JTAG, Parallel Flash Tralover (FPP) z szybkim pasywnym układem hydraulicznym (PFL)

Przyciski, przełączniki, diody LED i wyświetlacze

Przycisk resetowania procesora

3 x przyciski użytkownika

8 mikroprzełączników

16 diod LED użytkownika (w tym osiem diod dwukolorowych)

3 diody LED PCIe

3 diody LED stanu HSMA

Wyświetlacz LCD o przekątnej 2 linii x 16 znaków

Agregat 2

Aria V GT FPGA: 5AGTFD7K3F40I3N

X64 DDR3 SDRAM - kontroler programowy (lub x32 - kontroler IP)

Port HSMC B (cztery kanały nadawczo-odbiorcze)

Port FMC (dziesięć kanałów nadajnika)

Most typu chip-chip z 29 wejściami LVDS i 29 wyjściami LVDS oraz transceiverami x8

Kanał szeregowy interfejs cyfrowy (SDI)

Złącze kamery Bull's Eye (kanał nadajnika-odbiornika o przepustowości 6 Gb/s)

Złącze kamery Bull's Eye (kanał nadajnika-odbiornika 10 Gb/s)

Złącze SMA (kanał nadajnika-odbiornika 10 Gb/s)

Konfiguracja: JTAG, Parallel Flash Tralover (FPP) z szybkim pasywnym układem hydraulicznym (PFL)

Przyciski, przełączniki, diody LED i wyświetlacze

Przycisk resetowania procesora

3 x przyciski użytkownika

8 mikroprzełączników

16 diod LED użytkownika (w tym osiem diod dwukolorowych)

Kontroler systemowy EPM2210GF324

Wbudowany kabel do pobierania USB-Blaster II EPM570GM100

Taktowanie: Oscylator 50 MHz i 145 MHz

Programowalne oscylatory o częstotliwości 100 MHz i 4 wyjścia

Wejście SMA (LVPECL)

Zasilanie: Gniazdo zasilania (prąd stały) laptopa, złącze krawędziowe PCIe

Monitorowanie systemu, zasilanie: (Napięcie, prąd i moc), na jednostkę na szynę

W zestawie

Karty pętli zwrotnej i debug HSMC, zestaw montażowy Samtec's Bull Eye, kable, dokumentacja, oprogramowanie

.

FPGA to urządzenie półprzewodnikowe składające się z Matrix Configurable Logic Blocks (CLB) połączonych przez programowalne łączniki. Użytkownik określa te połączenia poprzez programowanie SRAM. CLB może być prosty (ORAZ, LUB Gates, itp.) lub złożony (blok pamięci RAM). Układ FPGA umożliwia wprowadzanie zmian w konstrukcji nawet po przylutowaniu urządzenia do płytki drukowanej.

Dane techniczne

Atrybut | Parametr |

|---|---|

| Technologia logiki programowanej | FPGA |

| Rodzaj zestawu | Zestaw uruchomieniowy |

| Symbol układu | 5AGTFD7K3F40I3N |

| Nazwa zestawu | Arria V GT |

- Nr art. RS:

- 778-5354

- Nr części producenta:

- DK-DEV-5AGTD7N

- Producent:

- Altera