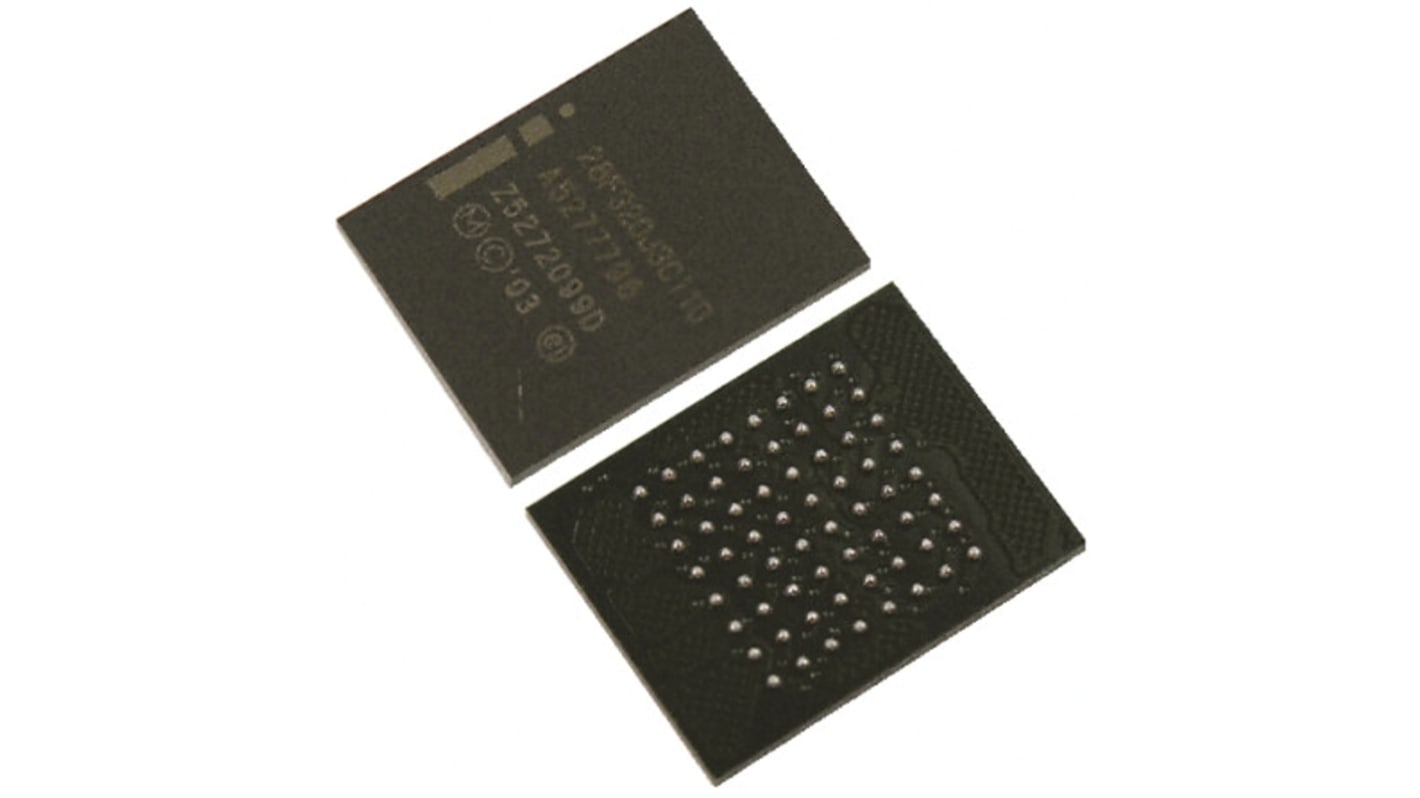

Złożony programowalny układ logiczny (CPLD) Altera MAX V MBGA 64 -pinowy komórki makro: 32

- Nr art. RS:

- 830-3650

- Nr części producenta:

- 5M40ZM64C5N

- Producent:

- Altera

Przy zakupie hurtowym dostępna zniżka

Suma częściowa (1 sztuka)*

4,37 zł

(bez VAT)

5,38 zł

(z VAT)

Informacje o zapasach są obecnie niedostępne - Sprawdź ponownie później

Produkty | Za jednostkę |

|---|---|

| 1 - 9 | 4,37 zł |

| 10 - 19 | 4,23 zł |

| 20 + | 4,14 zł |

*cena orientacyjna

- Nr art. RS:

- 830-3650

- Nr części producenta:

- 5M40ZM64C5N

- Producent:

- Altera

Specyfikacje

Informacje techniczne

Atesty i certyfikaty

Szczegółowe dane produktu

Znajdź produkty o zbliżonych parametrach, wybierając jeden lub więcej atrybutów.

Zaznacz wszystkie | Atrybut | Wartość |

|---|---|---|

| Marka | Altera | |

| Rodzina układów | MAX V | |

| Liczba komórek makro | 32 | |

| Liczba wejść/wyjść użytkownika | 30 | |

| Typ pamięci | Flash | |

| Liczba bloków/elementów logicznych | 40 | |

| Możliwość programowania w systemie | W systemie | |

| Typ montażu | Montaż powierzchniowy | |

| Typ opakowania | MBGA | |

| Minimalna temperatura robocza | 0°C | |

| Maksymalna temperatura robocza | +85°C | |

| Liczba styków | 64 | |

| Opóźnienie propagacji | 14ns | |

| Możliwość sterowania poszczególnymi wyjściami | Tak | |

| Wymiary | 4.5 x 4.5 x 1.05mm | |

| Wysokość | 1.05mm | |

| Maksymalne robocze napięcie zasilania | 1,89 V | |

| Długość | 4.5mm | |

| Szerokość | 4.5mm | |

| Minimalne robocze napięcie zasilania | 1,71 V | |

| Możliwość ponownego zaprogramowania | Tak | |

| Warunek testu opóźnienia propagacji | 10pF | |

| Zaznacz wszystkie | ||

|---|---|---|

Marka Altera | ||

Rodzina układów MAX V | ||

Liczba komórek makro 32 | ||

Liczba wejść/wyjść użytkownika 30 | ||

Typ pamięci Flash | ||

Liczba bloków/elementów logicznych 40 | ||

Możliwość programowania w systemie W systemie | ||

Typ montażu Montaż powierzchniowy | ||

Typ opakowania MBGA | ||

Minimalna temperatura robocza 0°C | ||

Maksymalna temperatura robocza +85°C | ||

Liczba styków 64 | ||

Opóźnienie propagacji 14ns | ||

Możliwość sterowania poszczególnymi wyjściami Tak | ||

Wymiary 4.5 x 4.5 x 1.05mm | ||

Wysokość 1.05mm | ||

Maksymalne robocze napięcie zasilania 1,89 V | ||

Długość 4.5mm | ||

Szerokość 4.5mm | ||

Minimalne robocze napięcie zasilania 1,71 V | ||

Możliwość ponownego zaprogramowania Tak | ||

Warunek testu opóźnienia propagacji 10pF | ||

.

Powiązane linki

- Złożony programowalny układ logiczny (CPLD) Altera MAX 3000A TQFP 44 -pinowy komórki makro: 32

- Złożony programowalny układ logiczny (CPLD) Altera MAX 3000A PLCC 44 -pinowy komórki makro: 32

- Złożony programowalny układ logiczny (CPLD) Altera MAX 7000 PLCC 44 -pinowy komórki makro: 64

- Złożony programowalny układ logiczny Altera EPM1270M256C5N MAX II MBGA 256-pinowy komórki makro: 980 212 1270 6.2 ns

- Złożony programowalny układ logiczny Altera MAX II MBGA 256-pinowy komórki makro: 980 212 1270 6.2 ns Możliwość

- Układ CPLD Altera MAX V EQFP 64 -pinowy komórki makro: 128

- Złożony programowalny układ logiczny Altera 5M160ZT100C4N MAX V TQFP 100-pinowy komórki makro: 128 79 160 7.9 ns

- Złożony programowalny układ logiczny Altera EPM1270T144C5N MAX II TQFP 144-pinowy komórki makro: 980 116 127 10 ns