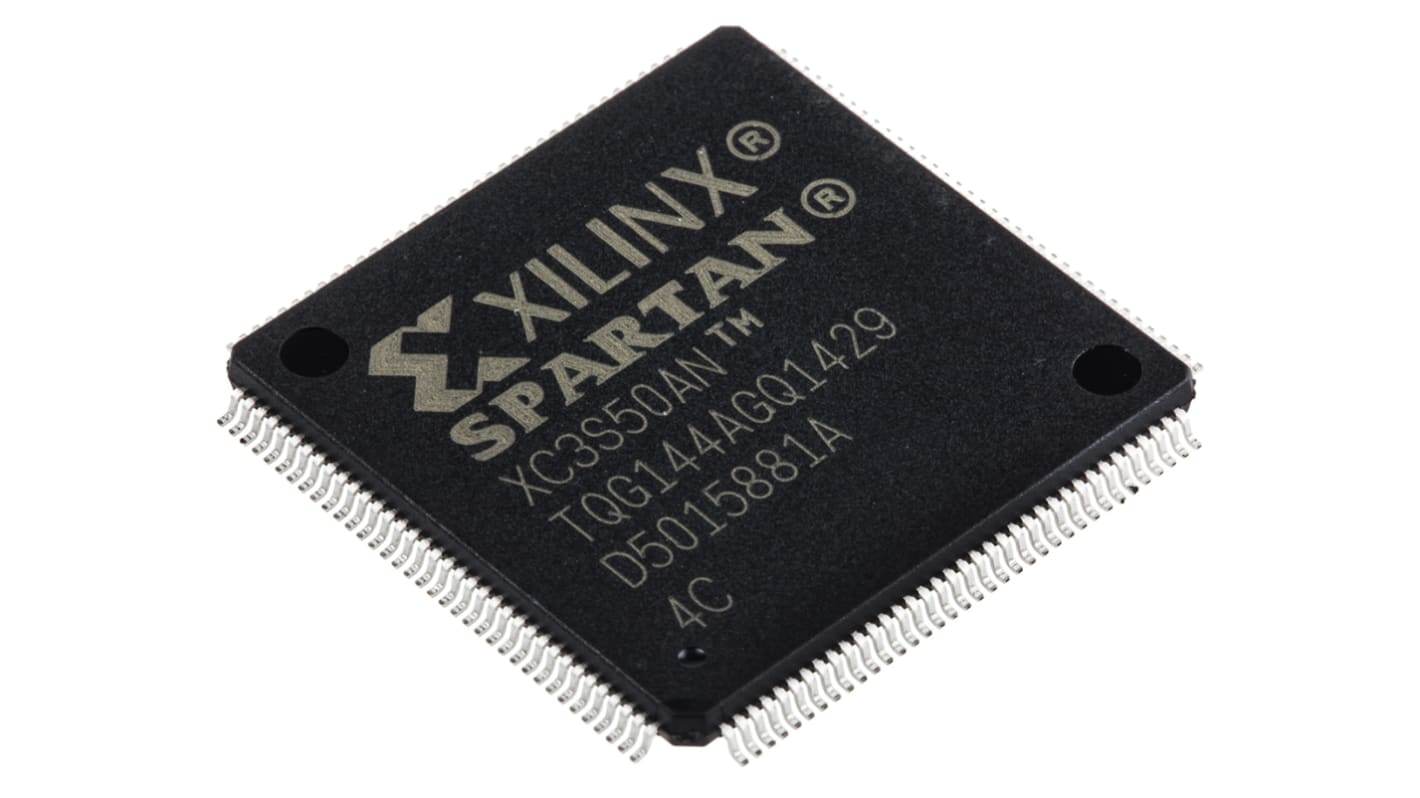

FPGA XC3S50AN-4TQG144C Spartan-3AN, 144-Pin, 1584-CLB, 11264bit, TQFP, Xilinx

- Nr art. RS:

- 697-2879

- Nr części producenta:

- XC3S50AN-4TQG144C

- Producent:

- Xilinx

Niedostępny

Wkrótce artykuł zostanie wycofany z oferty

- Nr art. RS:

- 697-2879

- Nr części producenta:

- XC3S50AN-4TQG144C

- Producent:

- Xilinx

Specyfikacje

Informacje techniczne

Atesty i certyfikaty

Szczegółowe dane produktu

Znajdź produkty o zbliżonych parametrach, wybierając jeden lub więcej atrybutów.

Zaznacz wszystkie | Atrybut | Wartość |

|---|---|---|

| Marka | Xilinx | |

| Rodzina układów | Spartan-3AN | |

| Liczba bramek logicznych | 50000 | |

| Liczba komórek logicznych | 1584 | |

| Liczba jednostek logicznych | 1584 | |

| Liczba krotników | 3 (18 x 18) | |

| Typ montażu | Montaż powierzchniowy | |

| Typ opakowania | TQFP | |

| Liczba styków | 144 | |

| Liczba bitów pamięci RAM | 11264bit | |

| Wymiary | 20 x 20 x 1.4mm | |

| Wysokość | 1.4mm | |

| Długość | 20mm | |

| Minimalna temperatura robocza | 0 °C | |

| Maksymalna temperatura robocza | +85 °C | |

| Maksymalne robocze napięcie zasilania | 1.26 V | |

| Szerokość | 20mm | |

| Minimalne robocze napięcie zasilania | 1.14 V | |

| Zaznacz wszystkie | ||

|---|---|---|

Marka Xilinx | ||

Rodzina układów Spartan-3AN | ||

Liczba bramek logicznych 50000 | ||

Liczba komórek logicznych 1584 | ||

Liczba jednostek logicznych 1584 | ||

Liczba krotników 3 (18 x 18) | ||

Typ montażu Montaż powierzchniowy | ||

Typ opakowania TQFP | ||

Liczba styków 144 | ||

Liczba bitów pamięci RAM 11264bit | ||

Wymiary 20 x 20 x 1.4mm | ||

Wysokość 1.4mm | ||

Długość 20mm | ||

Minimalna temperatura robocza 0 °C | ||

Maksymalna temperatura robocza +85 °C | ||

Maksymalne robocze napięcie zasilania 1.26 V | ||

Szerokość 20mm | ||

Minimalne robocze napięcie zasilania 1.14 V | ||