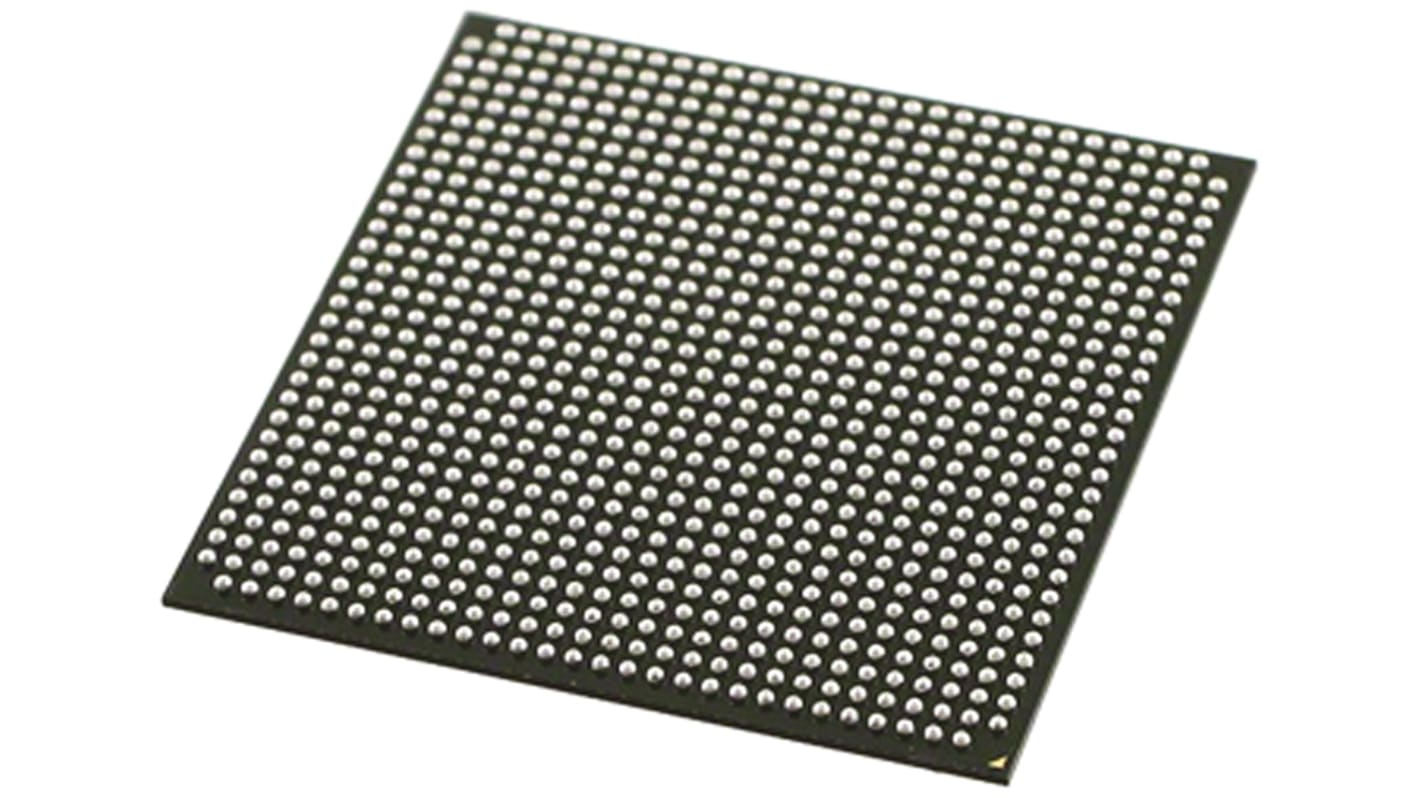

FPGA 5CSEMA6F31C8N Cyclone V SE 896-pinowy, 110000-CLB, 5761K, 1,8 → 3,3 V, FBGA, Altera

- Nr art. RS:

- 830-3574

- Nr części producenta:

- 5CSEMA6F31C8N

- Producent:

- Altera

Obecnie niedostępne

Przepraszamy, nie mamy informacji, czy ten produkt będzie jeszcze dostępny w magazynie. Zostanie on wkrótce usunięty z oferty RS.

- Nr art. RS:

- 830-3574

- Nr części producenta:

- 5CSEMA6F31C8N

- Producent:

- Altera

Specyfikacje

Informacje techniczne

Atesty i certyfikaty

Szczegółowe dane produktu

Znajdź produkty o zbliżonych parametrach, wybierając jeden lub więcej atrybutów.

Zaznacz wszystkie | Atrybut | Wartość |

|---|---|---|

| Marka | Altera | |

| Rodzina układów | Cyclone V SE | |

| Liczba bramek logicznych | 110000 | |

| Liczba komórek logicznych | 110000 | |

| Liczba jednostek logicznych | 41509 | |

| Przydzielony procesor DSP | Tak | |

| Liczba rejestrów | 166036 | |

| Liczba krotników | 224 (18 x 18) | |

| Typ montażu | Montaż powierzchniowy | |

| Typ opakowania | FBGA | |

| Liczba styków | 896 | |

| Liczba bitów pamięci RAM | 5761K | |

| Długość | 31mm | |

| Minimalna temperatura robocza | 0°C | |

| Maksymalne robocze napięcie zasilania | 3,3 V | |

| Minimalne robocze napięcie zasilania | 1,8 V | |

| Szerokość | 31mm | |

| Maksymalna temperatura robocza | +85°C | |

| Zaznacz wszystkie | ||

|---|---|---|

Marka Altera | ||

Rodzina układów Cyclone V SE | ||

Liczba bramek logicznych 110000 | ||

Liczba komórek logicznych 110000 | ||

Liczba jednostek logicznych 41509 | ||

Przydzielony procesor DSP Tak | ||

Liczba rejestrów 166036 | ||

Liczba krotników 224 (18 x 18) | ||

Typ montażu Montaż powierzchniowy | ||

Typ opakowania FBGA | ||

Liczba styków 896 | ||

Liczba bitów pamięci RAM 5761K | ||

Długość 31mm | ||

Minimalna temperatura robocza 0°C | ||

Maksymalne robocze napięcie zasilania 3,3 V | ||

Minimalne robocze napięcie zasilania 1,8 V | ||

Szerokość 31mm | ||

Maksymalna temperatura robocza +85°C | ||

Cyclone FPGA Altera

.

FPGA to urządzenie półprzewodnikowe składające się z Matrix Configurable Logic Blocks (CLB) połączonych przez programowalne łączniki. Użytkownik określa te połączenia poprzez programowanie SRAM. CLB może być prosty (ORAZ, LUB Gates, itp.) lub złożony (blok pamięci RAM). Układ FPGA umożliwia wprowadzanie zmian w konstrukcji nawet po przylutowaniu urządzenia do płytki drukowanej.