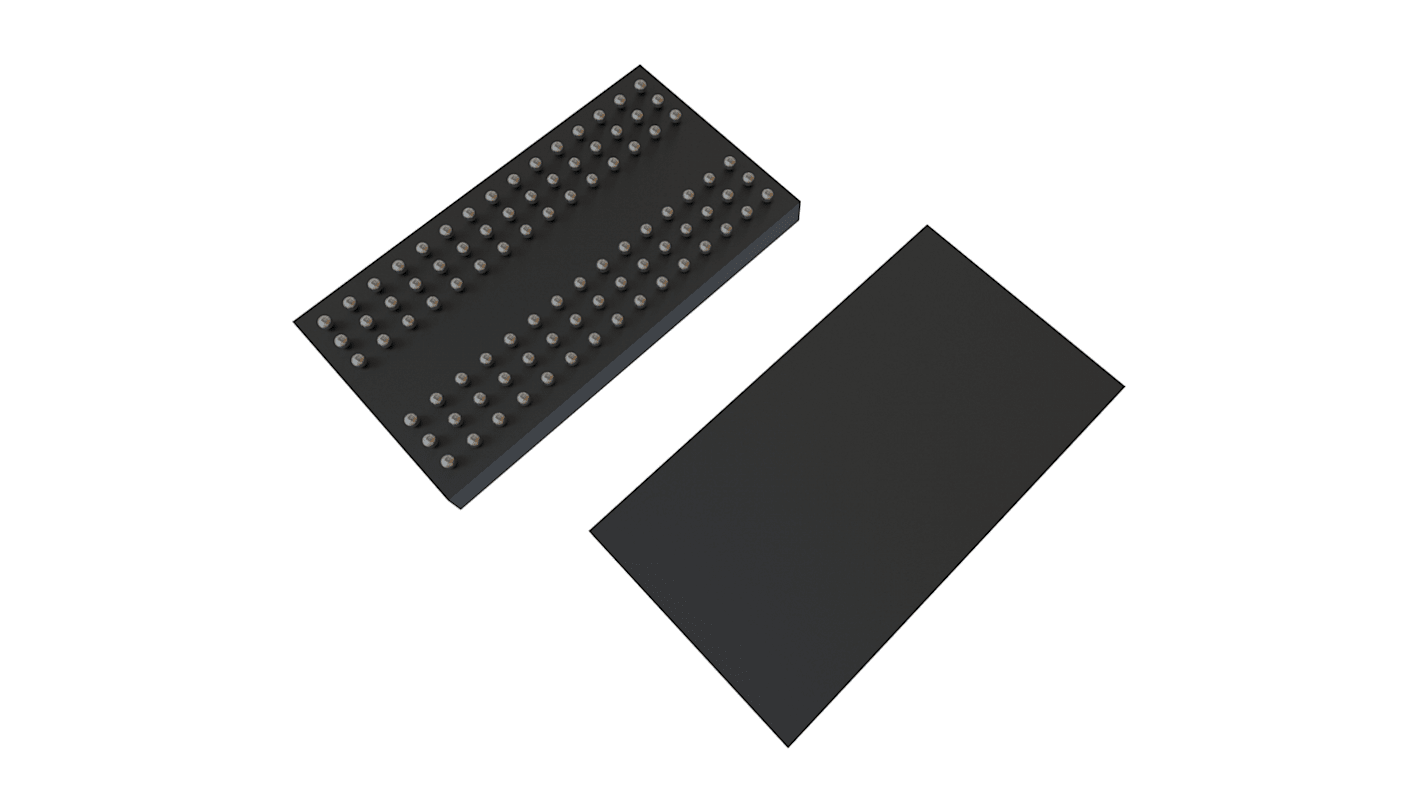

Winbond DDR2 SDRAM 128 MB 84-pinowy TFBGA Powierzchnia 16 bit 95 °C -40 °C

- Nr art. RS:

- 188-2580

- Nr części producenta:

- W9712G6KB25I

- Producent:

- Winbond

Suma częściowa (1 tacka po 209 sztuk/i)*

1 667,611 zł

(bez VAT)

2 051,126 zł

(z VAT)

DARMOWA wysyłka dla zamówień o wartości powyżej 330,00 zł

Tymczasowo niedostępny

- Dostępne od 21 września 2026

Potrzebujesz więcej? Wprowadź ilość, kliknij „Sprawdź daty dostawy” dla szczegółów dostawy.

Produkty | Za jednostkę | Za Tackę* |

|---|---|---|

| 209 + | 7,979 zł | 1 667,61 zł |

*cena orientacyjna

- Nr art. RS:

- 188-2580

- Nr części producenta:

- W9712G6KB25I

- Producent:

- Winbond

Specyfikacje

Informacje techniczne

Atesty i certyfikaty

Szczegółowe dane produktu

Znajdź produkty o zbliżonych parametrach, wybierając jeden lub więcej atrybutów.

Zaznacz wszystkie | Atrybut | Wartość |

|---|---|---|

| Marka | Winbond | |

| Rozmiar pamięci | 128MB | |

| Typ produktu | DDR2 SDRAM | |

| Szerokość magistrali danych | 16bit | |

| Szerokość magistrali adresowej | 15bit | |

| Liczba bitów w słowie | 8 | |

| Maksymalny czas dostępu swobodnego | 0.4ns | |

| Liczba słów | 16M | |

| Typ montażu | Powierzchnia | |

| Typ obudowy | TFBGA | |

| Liczba styków | 84 | |

| Minimalna temperatura robocza | -40°C | |

| Maksymalna temperatura robocza | 95°C | |

| Seria | W9712G6KB | |

| Długość | 12.6mm | |

| Wysokość | 0.8mm | |

| Normy/Zatwierdzenia | RoHS | |

| Norma motoryzacyjna | Nie | |

| Minimalne napięcie zasilania | 1.7V | |

| Maksymalne napięcie zasilania | 1.9V | |

| Prąd zasilania | 135mA | |

| Zaznacz wszystkie | ||

|---|---|---|

Marka Winbond | ||

Rozmiar pamięci 128MB | ||

Typ produktu DDR2 SDRAM | ||

Szerokość magistrali danych 16bit | ||

Szerokość magistrali adresowej 15bit | ||

Liczba bitów w słowie 8 | ||

Maksymalny czas dostępu swobodnego 0.4ns | ||

Liczba słów 16M | ||

Typ montażu Powierzchnia | ||

Typ obudowy TFBGA | ||

Liczba styków 84 | ||

Minimalna temperatura robocza -40°C | ||

Maksymalna temperatura robocza 95°C | ||

Seria W9712G6KB | ||

Długość 12.6mm | ||

Wysokość 0.8mm | ||

Normy/Zatwierdzenia RoHS | ||

Norma motoryzacyjna Nie | ||

Minimalne napięcie zasilania 1.7V | ||

Maksymalne napięcie zasilania 1.9V | ||

Prąd zasilania 135mA | ||

W9712G6KB jest 128-bitową pamięcią DDR2 SDRAM i zapewnia szybkość przełączania między -25, 25I i -3.

Architektura podwójnej prędkości danych: dwa transfery danych na cykl zegara

Stopień opóźnienia CAS: 3, 4, 5 i 6

Długość paczki impulsów: 4 i 8

Dwukierunkowe, różnicowe stroboskopy danych (DQS i /DQS) są przesyłane/odbierane z danymi

Wyrównane do krawędzi z danymi odczytu i wyrównane do środka z danymi zapisu

DLL synchronizuje przesyły DQ i DQS z zegarem

Różnicowe wejścia zegara (CLK i /CLK)

Maski danych (DM) dla danych zapisu

Polecenia wprowadzane na każdej dodatniej krawędzi CLK, dane i maski danych odnoszą się do obu krawędzi /DQS

Programowalne opóźnienia dodatków dekretowane /CAS są obsługiwane w celu zapewnienia wydajności magistrali poleceń i danych

Średni czas oczekiwania = dodatkowe opóźnienie plus opóźnienie CAS (RL = AL + CL)

Regulacja impedancji przez sterownik poza układem (OCD) i zakończenie na matrycy (ODT) dla lepszej jakości sygnału

Automatyczne ładowanie wstępne paczek impulsów odczytu i zapisu

Tryby automatycznego odświeżania i samoczynnego odświeżania

Wstępnie obciążone wyłączenie zasilania i aktywne wyłączenie zasilania

Zapisz maskę danych

Opóźnienie zapisu = Przeczytaj opóźnienie - 1 (WL = RL - 1)

Interfejs: SSTL_18

Powiązane linki

- Winbond DDR2 SDRAM W9712G6KB25I 128 MB 84-pinowy TFBGA Powierzchnia 16 bit 95 °C -40 °C

- Winbond SDRAM 512 MB 84-pinowy VFBGA Powierzchnia 16 bit 95 °C -40 °C

- Winbond SDRAM W9751G6NB25I 512 MB 84-pinowy VFBGA Powierzchnia 16 bit 95 °C -40 °C

- Winbond SDRAM 128 MB 54-pinowy TSOP Powierzchnia 16 bit 85 °C -40 °C

- Winbond SDRAM W9812G6KH-6I 128 MB 54-pinowy TSOP Powierzchnia 16 bit 85 °C -40 °C

- Pamięć DDR2 SDRAM 84-pinowy 800MHz DDR2, Montaż powierzchniowy

- Winbond SDRAM 1 GB 84-pinowy Powierzchnia 16 bit 95 °C -40 °C

- Winbond SDRAM W971GG6NB25I 1 GB 84-pinowy Powierzchnia 16 bit 95 °C -40 °C