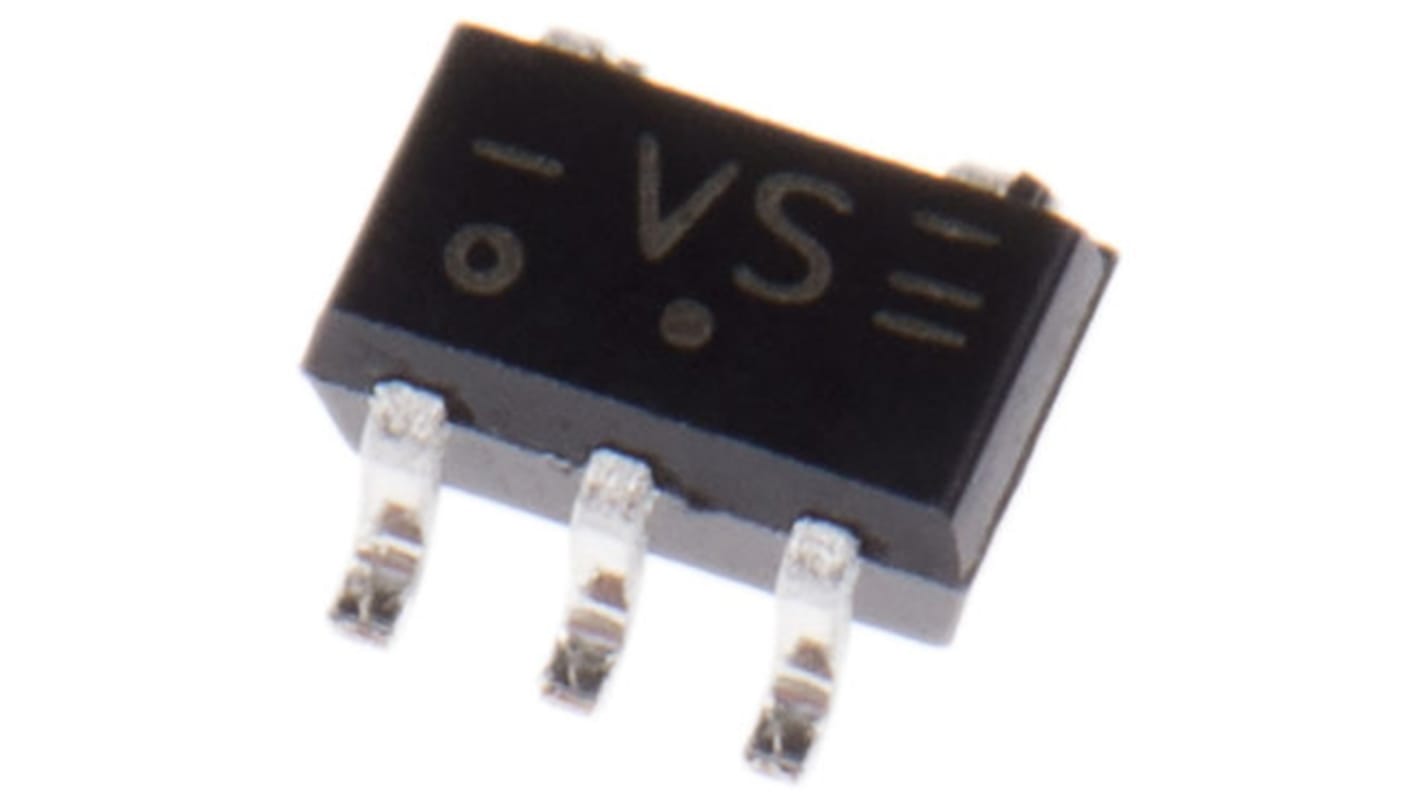

Nexperia Bramka logiczna 74LVC1G08GW,125 AND 1 Powierzchnia TSSOP wejścia na bramkę: 2 5-pinowy

- Nr art. RS:

- 510-201

- Nr części producenta:

- 74LVC1G08GW,125

- Producent:

- Nexperia

Suma częściowa (1 opakowanie po 50 sztuk/i)*

8,20 zł

(bez VAT)

10,10 zł

(z VAT)

DARMOWA wysyłka dla zamówień o wartości powyżej 330,00 zł

W magazynie

- 50 szt. do wysyłki z innej lokalizacji

- Dodatkowe 5600 szt. dostępne od 04 maja 2026

Potrzebujesz więcej? Wprowadź ilość, kliknij „Sprawdź daty dostawy” dla szczegółów dostawy.

Produkty | Za jednostkę | Za Opakowanie* |

|---|---|---|

| 50 + | 0,164 zł | 8,20 zł |

*cena orientacyjna

- Nr art. RS:

- 510-201

- Nr części producenta:

- 74LVC1G08GW,125

- Producent:

- Nexperia

Specyfikacje

Informacje techniczne

Atesty i certyfikaty

Szczegółowe dane produktu

Znajdź produkty o zbliżonych parametrach, wybierając jeden lub więcej atrybutów.

Zaznacz wszystkie | Atrybut | Wartość |

|---|---|---|

| Marka | Nexperia | |

| Typ produktu | Bramka logiczna | |

| Funkcja logiczna | AND | |

| Typ montażu | Powierzchnia | |

| Liczba elementów | 1 | |

| Liczba wejść na bramkę | 2 | |

| Wejście przerzutnika Schmitta | Nie | |

| Typ obudowy | TSSOP | |

| Liczba styków | 5 | |

| Seria układów logicznych | LVC | |

| Typ wejścia | CMOS | |

| Maksymalny prąd wyjściowy wysokiego poziomu | -32mA | |

| Minimalna temperatura robocza | -40°C | |

| Maksymalny czas opóźnienia propagacji @ CL | 5.5ns | |

| Maksymalna temperatura robocza | 125°C | |

| Normy/Zatwierdzenia | No | |

| Maksymalne napięcie zasilania | 5.5V | |

| Długość | 2.25mm | |

| Minimalne napięcie zasilania | 1.65V | |

| Wysokość | 1mm | |

| Maksymalny prąd wyjściowy niskiego poziomu | 32mA | |

| Norma motoryzacyjna | Nie | |

| Zaznacz wszystkie | ||

|---|---|---|

Marka Nexperia | ||

Typ produktu Bramka logiczna | ||

Funkcja logiczna AND | ||

Typ montażu Powierzchnia | ||

Liczba elementów 1 | ||

Liczba wejść na bramkę 2 | ||

Wejście przerzutnika Schmitta Nie | ||

Typ obudowy TSSOP | ||

Liczba styków 5 | ||

Seria układów logicznych LVC | ||

Typ wejścia CMOS | ||

Maksymalny prąd wyjściowy wysokiego poziomu -32mA | ||

Minimalna temperatura robocza -40°C | ||

Maksymalny czas opóźnienia propagacji @ CL 5.5ns | ||

Maksymalna temperatura robocza 125°C | ||

Normy/Zatwierdzenia No | ||

Maksymalne napięcie zasilania 5.5V | ||

Długość 2.25mm | ||

Minimalne napięcie zasilania 1.65V | ||

Wysokość 1mm | ||

Maksymalny prąd wyjściowy niskiego poziomu 32mA | ||

Norma motoryzacyjna Nie | ||

Rodzina 74LVC1G/74LVC2G.

Układy logiczne CMOS o niskim napięciu zasilania

Pakiet pojedynczej bramki

Napięcie robocze: 1,65 do 5,5 V.

Kompatybilność: Wejście LVTTL/TTL, wyjście LVCMOS

Rodzina 74LVC

Powiązane linki

- Nexperia Bramka logiczna AND 1 Powierzchnia TSSOP wejścia na bramkę: 2 5-pinowy

- Nexperia Bramka logiczna 74AHCT1G08GV,125 AND 1 Powierzchnia TSSOP wejścia na bramkę: 2 5-pinowy

- Nexperia Bramka logiczna 74AHCT1G08GW,125 AND 1 Powierzchnia TSSOP wejścia na bramkę: 2 5-pinowy

- Nexperia Bramka logiczna 74HC1G08GW,125 AND 1 Powierzchnia TSSOP wejścia na bramkę: 2 5-pinowy Aktualne

- Nexperia Bramka logiczna AND 1 Powierzchnia TSSOP wejścia na bramkę: 2 5-pinowy Aktualne

- Nexperia Bramka logiczna 74AHC1G08GW,125 AND 1 Powierzchnia TSSOP-5 wejścia na bramkę: 2 5-pinowy CMOS

- Nexperia Bramka logiczna AND 4 Powierzchnia TSSOP wejścia na bramkę: 2 14-pinowy

- Nexperia Bramka logiczna AND Powierzchnia TSSOP-5 wejścia na bramkę: 2 5-pinowy Wejście przerzutnika Schmitta