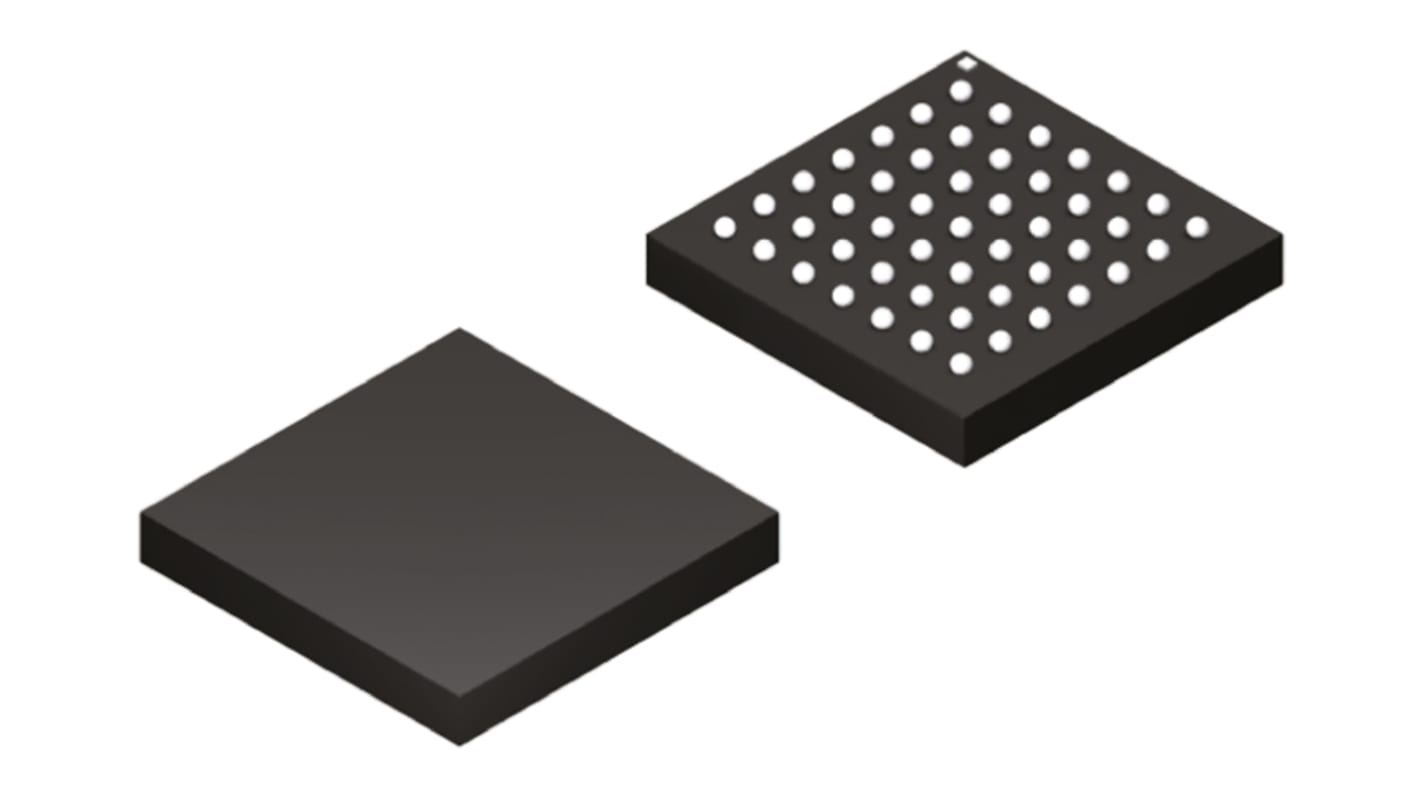

FPGA iCE40 LP/HX 49-pinowy, 1280-CLB, 64 kB, UCBGA, Lattice Semiconductor

- Nr art. RS:

- 168-4224

- Nr części producenta:

- ICE40LP1K-CM49

- Producent:

- Lattice Semiconductor

Obecnie niedostępne

Przepraszamy, nie mamy informacji, czy ten produkt będzie jeszcze dostępny w magazynie. Zostanie on wkrótce usunięty z oferty RS.

- Nr art. RS:

- 168-4224

- Nr części producenta:

- ICE40LP1K-CM49

- Producent:

- Lattice Semiconductor

Specyfikacje

Informacje techniczne

Atesty i certyfikaty

Szczegółowe dane produktu

Znajdź produkty o zbliżonych parametrach, wybierając jeden lub więcej atrybutów.

Zaznacz wszystkie | Atrybut | Wartość |

|---|---|---|

| Marka | Lattice Semiconductor | |

| Seria | iCE40 LP/HX | |

| Typ produktu | FPGA | |

| Liczba bramek logicznych | 1280 | |

| Liczba pętli | 160 | |

| Liczba rejestrów | 1280 | |

| Typ montażu | Powierzchnia | |

| Typ obudowy | UCBGA | |

| Minimalne napięcie zasilania | 1.14V | |

| Liczba styków | 49 | |

| Maksymalne napięcie zasilania | 1.26V | |

| Liczba bitów pamięci RAM | 64kB | |

| Minimalna temperatura robocza | -40°C | |

| Maksymalna temperatura robocza | 85°C | |

| Długość | 3mm | |

| Wysokość | 0.9mm | |

| Normy/Zatwierdzenia | Halogen Free | |

| Norma motoryzacyjna | Nie | |

| Zaznacz wszystkie | ||

|---|---|---|

Marka Lattice Semiconductor | ||

Seria iCE40 LP/HX | ||

Typ produktu FPGA | ||

Liczba bramek logicznych 1280 | ||

Liczba pętli 160 | ||

Liczba rejestrów 1280 | ||

Typ montażu Powierzchnia | ||

Typ obudowy UCBGA | ||

Minimalne napięcie zasilania 1.14V | ||

Liczba styków 49 | ||

Maksymalne napięcie zasilania 1.26V | ||

Liczba bitów pamięci RAM 64kB | ||

Minimalna temperatura robocza -40°C | ||

Maksymalna temperatura robocza 85°C | ||

Długość 3mm | ||

Wysokość 0.9mm | ||

Normy/Zatwierdzenia Halogen Free | ||

Norma motoryzacyjna Nie | ||

- Kraj pochodzenia:

- KR

Programowalne macierze bramkowe, Lattice Semiconductor

FPGA to urządzenie półprzewodnikowe składające się z Matrix Configurable Logic Blocks (CLB) połączonych przez programowalne łączniki. Użytkownik określa te połączenia poprzez programowanie SRAM. CLB może być prosty (ORAZ, LUB Gates, itp.) lub złożony (blok pamięci RAM). Układ FPGA umożliwia wprowadzanie zmian w konstrukcji nawet po przylutowaniu urządzenia do płytki drukowanej.

Powiązane linki

- FPGA iCE40 LP/HX 49-pinowy 64 kB Lattice Semiconductor

- FPGA iCE40 144-pinowy 80000 bit Lattice Semiconductor

- FPGA iCE40 100-pinowy 64000 bit Lattice Semiconductor

- FPGA iCE40HX4K-TQ144 iCE40 144-pinowy 80000 bit Lattice Semiconductor

- FPGA iCE40HX1K-VQ100 iCE40 100-pinowy 64000 bit Lattice Semiconductor

- FPGA Cyclone II 144-pinowy TQFP, Altera

- FPGA Cyclone III 484-pinowy FBGA, Altera

- FPGA Cyclone II 208-pinowy PQFP, Altera